|

NKC Forum |

| Autor | Thema: Warum funktioniert die SER? |

|---|---|

|

m.haardt Voll in Gange    ID # 93 |

Erstellt am 14. Februar 2021 13:12 (#1)

Erstellt am 14. Februar 2021 13:12 (#1)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo,

ich kriege es nicht hin, die SER mit dem Arduino als Busmaster anzusprechen. Registerzugriffe funktionieren, ich kann Daten senden, aber das Transmitter Ready Bit wird gelegentlich nicht gesetzt und dann hängt alles. Also befasste ich mich tiefer mit der Schaltung und kann nur noch staunen. Phi2 ist bei den 65er Bausteinen Takt und Strobe für Zugriffe in einem. Die Adressen, R/W und CS müssen anliegen, bevor Phi2 den Zugriff macht. Im Grunde könnte man Phi2 mit IORQ treiben. Man hat jedoch eine race condition, weil IORQ und RD/WR zeitgleich generiert werden. Also hat RDK IORQ mit der positiven Taktflanke verzögert. Gleichzeitig benutzt er RFSH, um Phi2 einen Takt zu geben. Das Datenblatt will tatsächlich, dass Phi2 ein Takt ist (maximale Zykluszeit 40 us). So weit, so gut. Die Timings stimmen nicht ganz, aber im Grunde ist alles ok. Gar nicht ok ist, dass RES nur wirkt, wenn es während Phi2 aktiv ist. Das steht aber nicht in allen Datenblätten. Der Baustein kriegt beim Z80 also nie ein Reset. Es gibt ein Software Reset, was aber nicht so vollständig wie ein Hardware Reset ist. Nun gut, das mag manche Probleme bei der Taktgenerierung mit einem Quarz erklären, scheint ansonsten aber nicht zu stören. Kein bisschen mehr ok ist es, dass der 68k kein Refresh generiert und damit Phi2 zu einem Strobe verkommt. Die SER funktioniert dennoch. Nun weiss ich vom 6522, dass der funktioniert, wenn man ihm mit IORQ als Phi2 betreibt. Man kann dann halt nur den Timer nicht mehr benutzen, weil es halt keinen Takt gibt, aber die race condition mit RD/WR macht nichts aus, was mir sagt, dass RD/WR erst verzögert ausgewertet wird. Es wird noch schlimmer: Der 68k generiert IORQ aus den Adressen, d.h. IORQ wird vor RD/WR aktiv. Und: Es gibt eine positive Taktflanke vor RD/WR, d.h. die Verzögerung ist unzureichend. Die SER funktioniert dennoch. Ich kann es mir nur so erklären, dass sie so langsam ist, dass das verzögerte RD/WR noch rechtzeitig kommt. Wahnsinn, dass das geht. Nun ließe sich das alles lösen, z.B. indem man ein Strobe aus RD/WR generiert und mit einem Monoflop um die geforderte Zeit verzögert. Damit entfällt die Abhängigkeit von Takt und IORQ-Timing. Aber es muss etwas geben, was der Baustein gar nicht liebt, und ich weiss nicht, was. Die Sache mit dem nicht erscheinenden Transmitter Ready Bit ist darum so interessant, weil die Version eines Herstellers (WD?) das als Bug hat. Der Hersteller hat den Chip bestimmt nicht neu entworfen, sondern ich vermute, dass sein Prozess das Timing veränderte und damit dieser Bug auftritt. Wenn ich die Bytezeit abwarte und einfach neue Daten sende, funktioniert das, und genau so muss man bei dem Chip mit dem Bug handeln. Wenn man das rausfindet, dann kriegt man die SER vermutlich auch mit dem 6502 ans Laufen. Nun bietet der Arduino einfachere Möglichkeiten, Timings auszuprobieren. Hat jemand Ideen? Ich will evtl. später heute mal ein Bild direkt am 6551 mit dem Logicanalyzer machen. Hier könnte ich wirklich etwas Hilfe brauchen. Michael |

Beiträge: 501 | Mitglied seit: April 2008 | IP-Adresse: nicht gespeichert | |

|

DerInder Fast schon Admin Seitenadmins    ID # 2 |

Erstellt am 14. Februar 2021 14:18 (#2)

Erstellt am 14. Februar 2021 14:18 (#2)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin Michael,

die SER hab ich eigentlich schon lange aufgegeben  Ein paar Punkte die in deiner Auflistung noch fehlen: Der Rockwell Chip (R6521) funktioniert scheinbar bei niemanden. Der Synertek Chip (SY6521) funktioniert teilweise. Am Z80 mit 8MHz und am 68008 mit 10MHz läuft es nicht. Am 68000 und dem 68020 hab ich die SER auch nicht zum laufen bekommen. Am 6502 hab ich es dann schon nichtmehr probiert, da man für den einiges an der SER umbauen müsste. Trotzdem interessiern mich deine Ergebnisse  PS: die SER2 läuft an allen NKC-Systemen  ----------------------- Gruß -=jens=- |

Beiträge: 912 | Mitglied seit: Juni 2004 | IP-Adresse: nicht gespeichert | |

|

m.haardt Voll in Gange    ID # 93 |

Erstellt am 14. Februar 2021 16:25 (#3)

Erstellt am 14. Februar 2021 16:25 (#3)

Zitat Zitat

PN PN  E-Mail E-Mail

Je höher der Takt, um so geringer wird die Verzögerung von Phi2 zu IORQ. Da sind Probleme zu erwarten. Darum halte ich es für klug, sich mit einem Monoflop vom Takt zu lösen. Alternativ könnte man den Takt mit dem zweiten Flipflop teilen, was ein geringerer Umbau wäre.

Der R6551AP funktioniert bei mir am Z80 mit 4 MHz und am 68008 (1 WS). Die SER2 finde ich nicht so toll, weil der Chip auch ein Exot ist und leider auch wie alle UARTs so seine Seltsamkeiten hat. 6551 kann man immer noch in China kaufen und bisher funktionierten die, die ich bekam. Eine SER mit 16550 wäre ideal, aber so oder so müsste man halt alle Software anfassen. Letztlich ist der Spaß am NKC aber doch das modulare System und ein 6551 kann offenbar funktionieren, wenn man es halbwegs richtig macht. Die Frage ist nur: Was macht der Arduino so falsch, dass sie nicht will? Könntest Du herausfinden, was beim Z80 mit 8 MHz und beim 68008 mit 10 MHz nicht funktioniert? Der Sendetest aus dem Buch ist mein Test: org 0100h ser equ 0f0h ;Basisadresse der SER (Jumper 000011) ser_dat equ ser+0 ser_sta equ ser+1 ser_cmd equ ser+2 ser_ctl equ ser+3 start1: ld a,1eh ;9600 Baud out (ser_ctl),a ld a,0bh ;no par enable out (ser_cmd),a ld c,01101010b ; testmuster loop1: in a,(ser_sta) ;status test and 10h ;transmitter ready jr z,loop1 ld a,c out (ser_dat),a ;auf datenport jr loop1 ;und widerholen ser equ $fffffff0 ; Basisadresse der SER (Jumper 000011) ser_dat equ (ser+0)*CPU ser_sta equ (ser+1)*CPU ser_cmd equ (ser+2)*CPU ser_ctl equ (ser+3)*CPU ds.b $400 ; 1k z.B. fuer exception table dc.l $5aa58001 ; Suchstring fuer Anfang dc.l 0,0,0,0,0,0,0 bra.w main ; Start-Trap mit RTS-Abschluss, unbenutzt bra.w main ; Kalt-Start main: move.b #$1e,(ser_ctl) ; 9600 Baud move.b #$0b,(ser_cmd) ; no par enable move.b #%01101010,d0 ; Testmuster (j) loop: move.b (ser_sta),d1 ; status test and.b #$10,d1 beq.s loop move.b d0,(ser_dat) ; auf datenport bra.s loop ; und wiederholen Michael |

Beiträge: 501 | Mitglied seit: April 2008 | IP-Adresse: nicht gespeichert | |

|

m.haardt Voll in Gange    ID # 93 |

Erstellt am 14. Februar 2021 18:16 (#4)

Erstellt am 14. Februar 2021 18:16 (#4)

Zitat Zitat

PN PN  E-Mail E-Mail

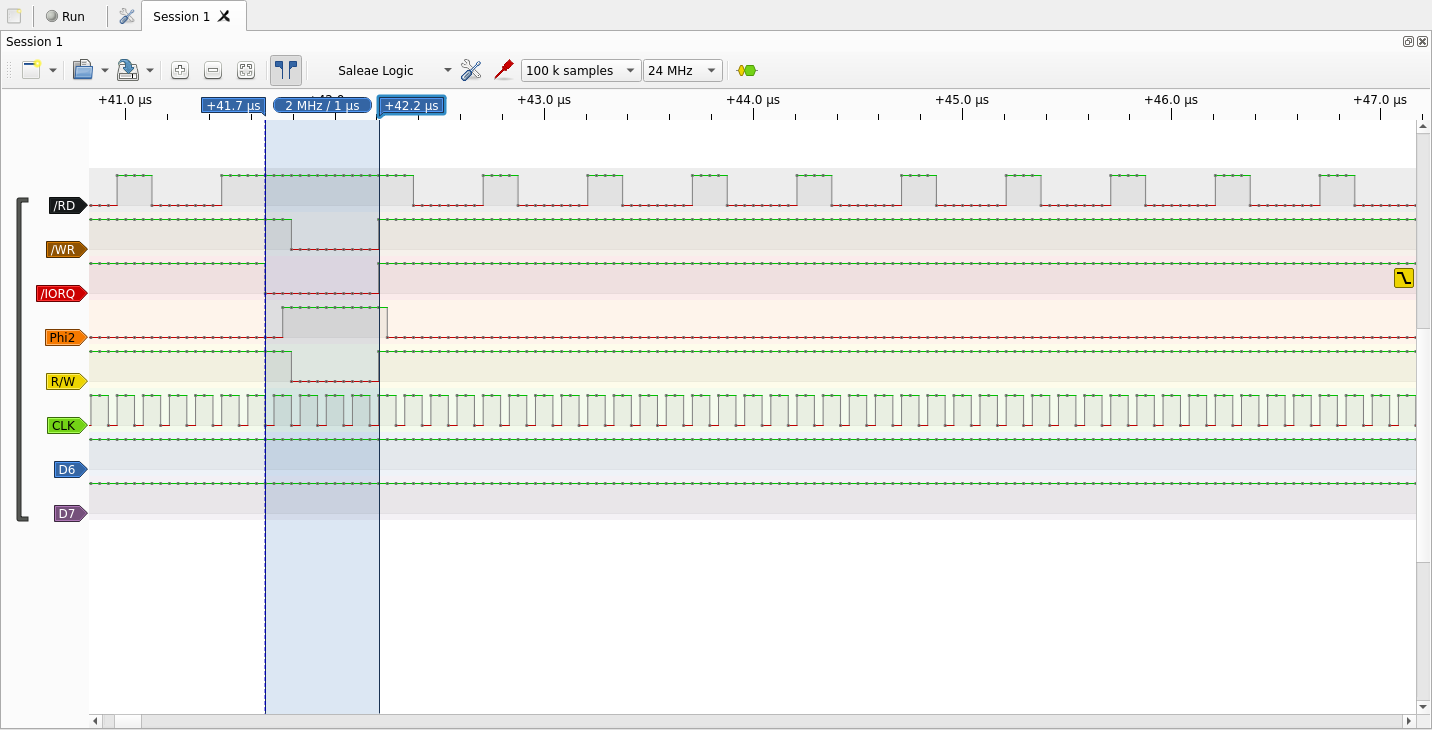

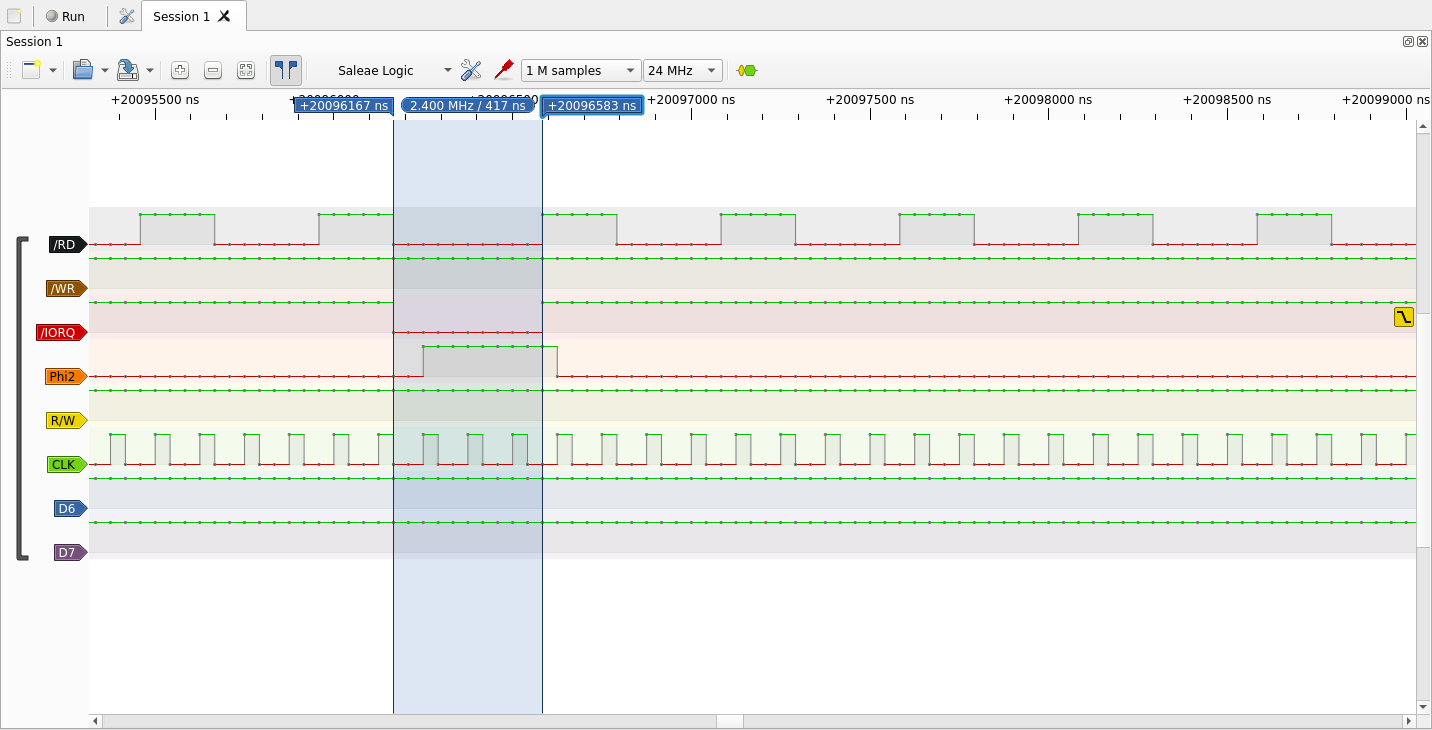

Ok, hier sind die Bilder. 68008 Schreibzugriff mit /IORQ deutlich vor /WR und als Ergebnis wechselt R/W nach Phi2. Die erste positive Flanke triggert das Flipflop, was aber erheblich propagation delay hat, so dass Phi2 verzögert wird. Vielleicht funktioniert es deswegen.

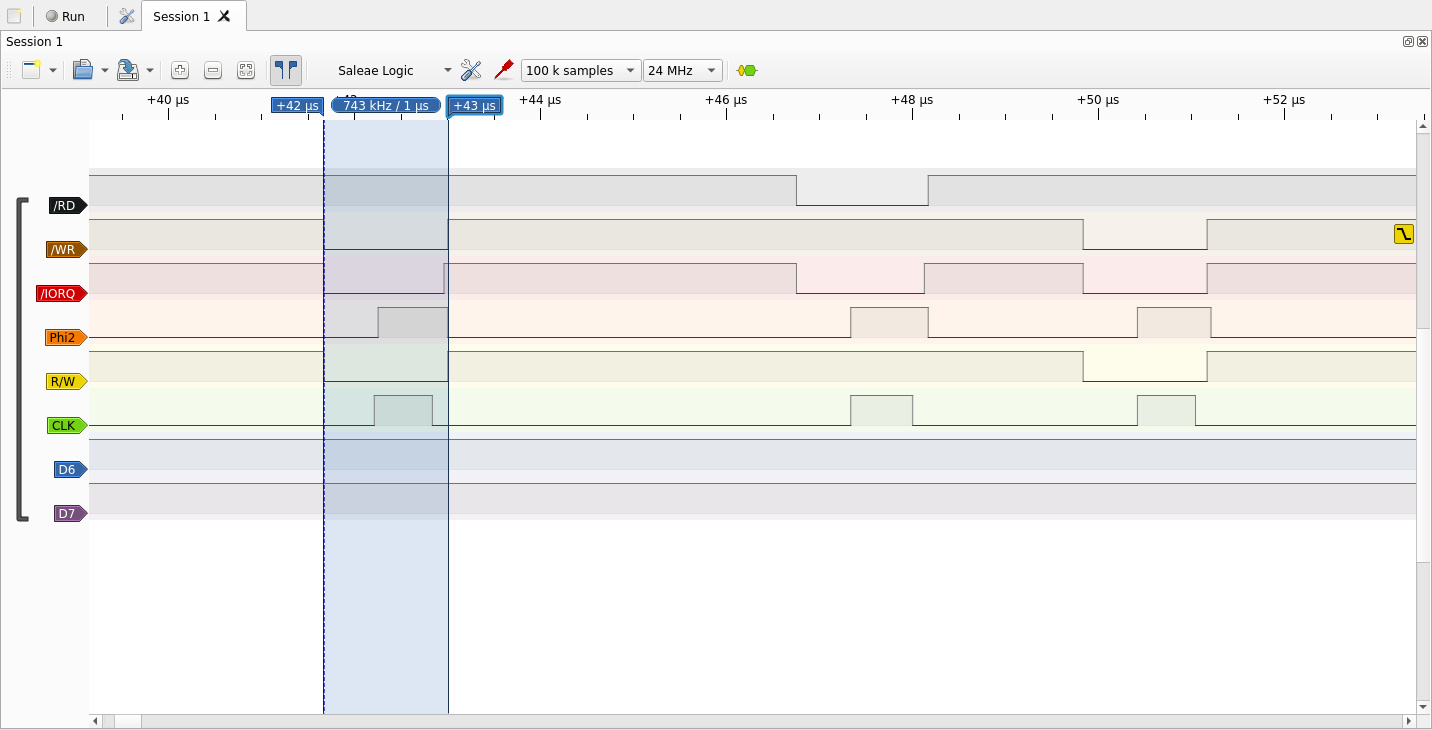

68008 Lesezugriff. Zu meinem Erstaunen ist /IORQ hier synchron mit /RD. Hier sieht man das Propagation delay beim Löschen des Flipflops. Vielleicht hätte ich den anderen LA nehmen sollen, der löst sowas besser auf.  Der 68008 funktioniert. Der Arduino hat das beschriebene Fehlerbild, dass Transmitter ready oft nicht erscheint. Ich kann aber CMD und CTL korrekt lesen. Hier erst ein Schreib- und dann ein Lesezugriff:  Natürlich ist alles langsamer, aber das Datenblatt erlaubt das. Michael |

Beiträge: 501 | Mitglied seit: April 2008 | IP-Adresse: nicht gespeichert |

| https://hschuetz.selfhost.eu | Boardregeln | Datenschutzerklärung

Tritanium Bulletin Board 1.8

© 2010–2021 Tritanium Scripts

Seite in 0,023368 Sekunden erstellt

16 Dateien verarbeitet

gzip Komprimierung eingeschaltet

2159,80 KiB Speichernutzung