|

NKC Forum |

| Autor | Thema: CTC-SIO-PIO | ||

|---|---|---|---|

|

Creep Voll in Gange    ID # 169 |

Erstellt am 29. Oktober 2017 12:54 (#41)

Erstellt am 29. Oktober 2017 12:54 (#41)

Zitat Zitat

PN PN  E-Mail E-Mail

Super! Die restlichen Prototypen schicke ich los, wenn ich wieder zuhause bin. Bin selber auf den Aufbau gespannt!

Gruß, Rene |

||

Beiträge: 651 | Mitglied seit: Januar 2017 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 29. Oktober 2017 13:11 (#42)

Erstellt am 29. Oktober 2017 13:11 (#42)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo Jens,

danke für den Hinweis. Dafür ist der Jumper ja da  Hab eben noch mal getestet: Die Z80 Grundeinstellung von JP4 gehört in Stellung 2! Sonst fühlt sich die PIO nicht vom RESET angesprochen und ein 3k3 zw. Anoden D1,2 nach +5V. VG Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

DerInder Fast schon Admin Seitenadmins    ID # 2 |

Erstellt am 29. Oktober 2017 13:56 (#43)

Erstellt am 29. Oktober 2017 13:56 (#43)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin Steffen,

zwei Dinge vermisse ich noch auf der Platine: 1. Einen Clockgenerator für die SIO! Denn aus dem CPU Takt kann man keine brauchbare Baudrate generieren. 2. Da wir ja u.U. Z80-CPUs mit unterschiedlichen Takten betreiben (ich z.B. mit 4, 8 und 10 MHz), wäre auch für die CTCs eine Taktquelle sinnvoll, damit man nicht jedesmal ein Programm anpassen muss. PS: Ich hab gerade das Datenblatt der SIO überflogen und festgestellt, das die SIO ja garkeine Baudrate generieren kann. Damit hat sich Punkt 1 natürlich erledigt, aber Punkt 2 finde ich daher um so wichtiger. ----------------------- Gruß -=jens=- |

||

Beiträge: 912 | Mitglied seit: Juni 2004 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 29. Oktober 2017 17:34 (#44)

Erstellt am 29. Oktober 2017 17:34 (#44)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin Jens, da würde sich ja eine programmierbare Taktquelle gut machen, damit man nicht immer einen Regler oder Schalter nachstellen muss. ...  ...eine CTC? ...eine CTC?Häufiger als die Taktrate der CPU wird man sicher die Baudrate verändern. Das geht entweder händisch oder wesentlich besser mit einer Programm-Eingabe. Ich könnte aber einen Jumper zur Verbindung des CTC2-TO2 mit TxC-A, RxC-A, Tx-B oder RxC-B einbauen. Wobei man u.U. jeweils TxC und RxC ohnehin brücken kann !? VG Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

DerInder Fast schon Admin Seitenadmins    ID # 2 |

Erstellt am 29. Oktober 2017 17:54 (#45)

Erstellt am 29. Oktober 2017 17:54 (#45)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin Steffen,

mit den Jumpern von CTC2 zur SIO ist schonmal sehr gut. Nur auch bei z.B. 4MHz Systemtakt bekommst du mit dem CTC kaum eine saubere Baudrate hin. Bei manchen würde es überhaupt nicht klappen. Daher der Vorschlag einen 1,8432 MHz Quarzoszillator mit vorsehen, daraus kann auch die CTC die gängigen Baudraten hinbekommen. Diesen könnte man dann auch per Jumper auf die jeweiligen CLK-Eingänge legen. ----------------------- Gruß -=jens=- |

||

Beiträge: 912 | Mitglied seit: Juni 2004 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 29. Oktober 2017 18:44 (#46)

Erstellt am 29. Oktober 2017 18:44 (#46)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo Jens,

an welche Baud-Raten denkst Du genau? Müsste Deiner Meinung nach SIO A und B mit unterschiedlichen Baud-Raten arbeiten? ...besser nicht! ...so langsam wird's eng! Vg Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

DerInder Fast schon Admin Seitenadmins    ID # 2 |

Erstellt am 29. Oktober 2017 19:46 (#47)

Erstellt am 29. Oktober 2017 19:46 (#47)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin Steffen,

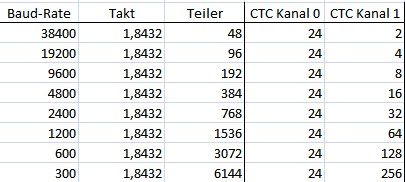

es brauchen keine unterschiedlichen Baudraten sein  Nur rechne mal durch, wie du z.B. 9600 Baud bei 4MHz hinbekommst. Das wären 4Mhz / 9600 Baud = 416,667, wenn du dann den Vorteiler zuschaltest (/256) kommst du auf einen Wert von 1,6 den du runterzählen müsstes. Das passt so irgendwie garnicht. Bei einem Takt von 1,8432 MHz müsste man nur um exakt 192 runterzählen um auf die 9600 Baud zu kommen. ----------------------- Gruß -=jens=- |

||

Beiträge: 912 | Mitglied seit: Juni 2004 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 29. Oktober 2017 20:55 (#48)

Erstellt am 29. Oktober 2017 20:55 (#48)

Zitat Zitat

PN PN  E-Mail E-Mail

...hmmm Jens, da hast Du wohl Recht!

Man braucht also einen 1,8432 MHz Oszilator und 2 CTC-Kanäle! Der CTC-Kanal 0 dient als Vorteiler und gibt seinen Takt an Kanal 1 und 2 weiter. Dann lassen sich im Kanal 1 und 2 "alle" Baud-Raten einstellen. Kann ich so machen! Kann ich mit dem Oszilator https://www.reichelt.de/Oszillatoren/OSZI-1-843200/3/index.html?ACTION=3&LA=446&ARTICLE=13674&GROUPID=3174&artnr=OSZI+1%2C843200&SEARCH=quarzoszillator direkt auf den CTC-Eingang gehen? Was meinst Du? VG Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

DerInder Fast schon Admin Seitenadmins    ID # 2 |

Erstellt am 29. Oktober 2017 21:02 (#49)

Erstellt am 29. Oktober 2017 21:02 (#49)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin Steffen,

das sollte so gehen. Den Quarzoszi kannst du ganz problemlos an den CTC Eingang hängen, der liefert auch TTL Pegel. ----------------------- Gruß -=jens=- |

||

Beiträge: 912 | Mitglied seit: Juni 2004 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 29. Oktober 2017 21:26 (#50)

Erstellt am 29. Oktober 2017 21:26 (#50)

Zitat Zitat

PN PN  E-Mail E-Mail

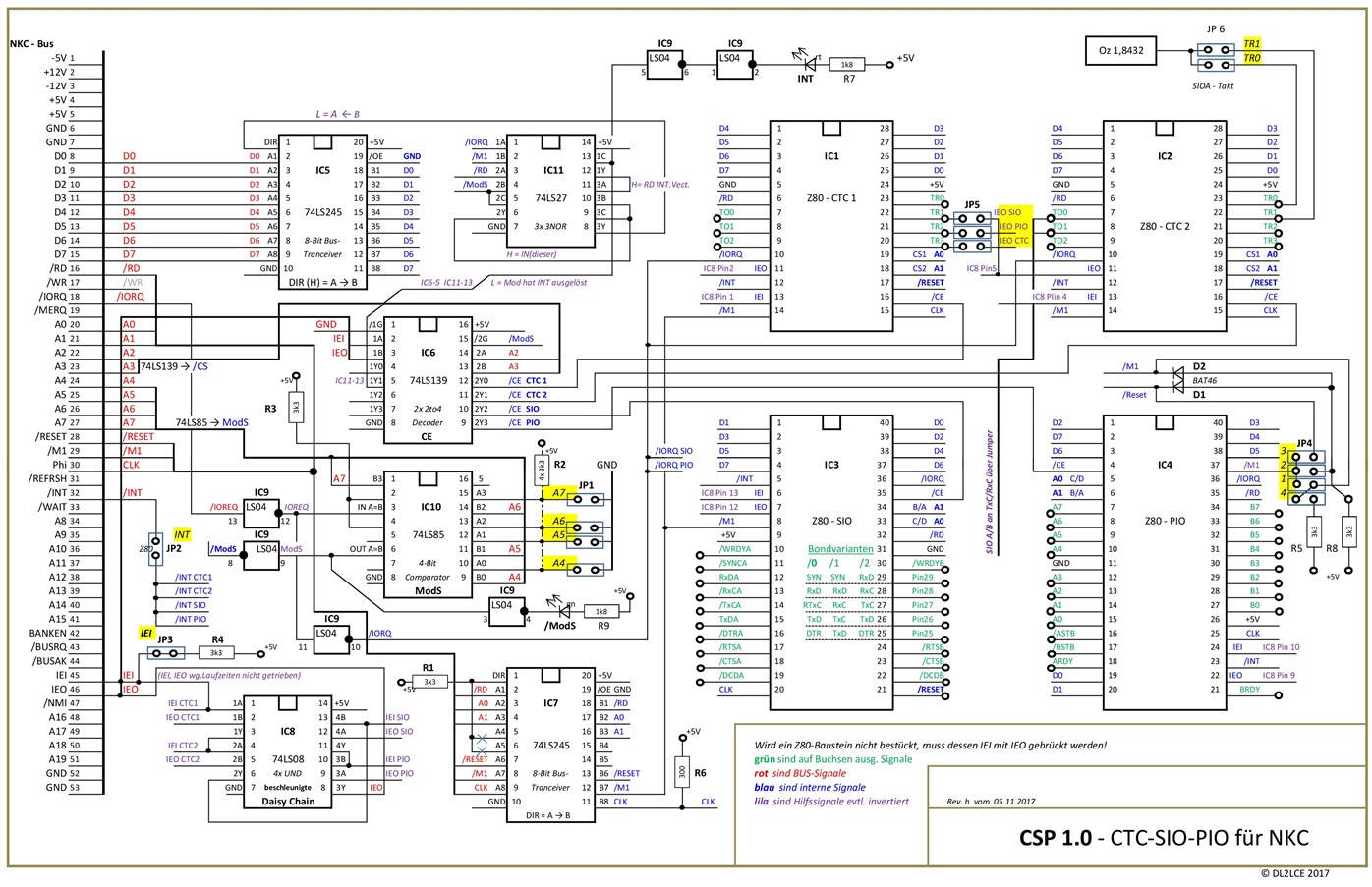

..jaaaa, dann könnte es so aussehen s.u.

Mir fällt aber gerade ein: "Wer nach allen Seiten offen ist, kann nicht ganz dicht sein!"  ...so langsam wird's unübersichtlich. VG Steffen  |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

DerInder Fast schon Admin Seitenadmins    ID # 2 |

Erstellt am 29. Oktober 2017 22:20 (#51)

Erstellt am 29. Oktober 2017 22:20 (#51)

Zitat Zitat

PN PN  E-Mail E-Mail

Sehr schön,

aber nenn es doch einfach komplex und nicht unübersichtlich

Wohl war, aber würde ich auch nie von mir behaupten  ----------------------- Gruß -=jens=- |

||

Beiträge: 912 | Mitglied seit: Juni 2004 | IP-Adresse: gespeichert | |||

|

netmercer Kennt sich schon aus   ID # 176 |

Erstellt am 30. Oktober 2017 20:30 (#52)

Erstellt am 30. Oktober 2017 20:30 (#52)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo Steffen.111,

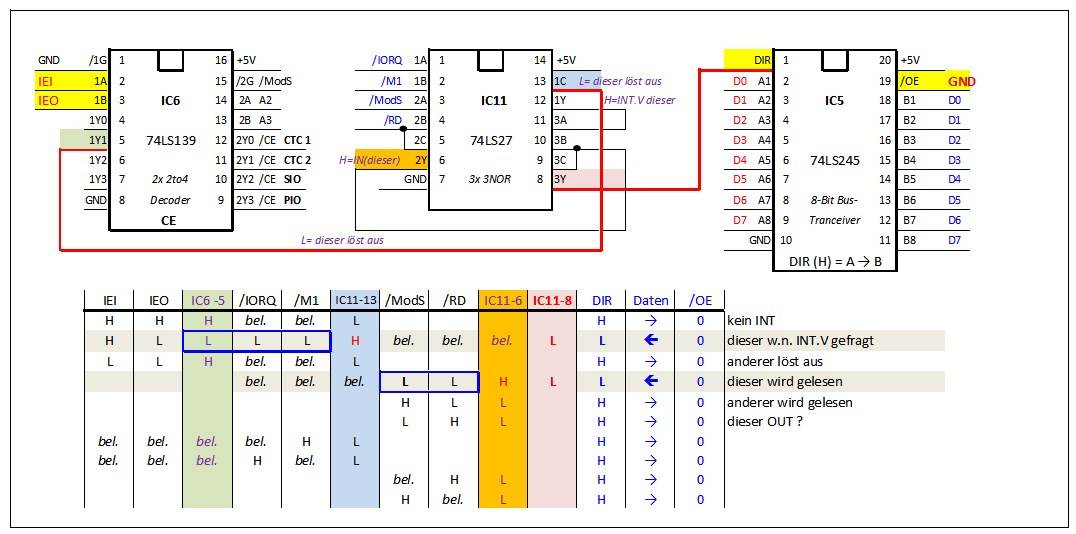

lese diesen Thread auch schon eine Weile mit und bin von Deiner Idee des CSP Boards begeistert. Soweit ich gelesen habe, werden erste Prototypen ja bereits getestet. Wurde dabei der Interruptmodus IM2, den CTC, PIO und SIO unterstützen, vielleicht auch schon angetestet? Nach lesen der Z80 Applikationnote zu diesem Thema, stehe ich nämlich etwas auf dem Schlauch: z80-interrupts.pdf Aber eventuell kann mir ja jemand die Funktionsweise verdeutlichen. Also, mein Verständnisproblem: Nachdem einer der Peripheriebausteine einen /INT ausgelöst hat, wird dieser nach Annahme durch den Z80 mit setzen von /M1 und /IORQ bestätigt. Jetzt legt der Peripheriebaustein, der den /INT ausgelöst hat seinen Interruptvektor auf den Datenbus und setzt IEO auf Low und unterbricht die Daisy Chain. Aus der Appl.note habe ich entnommen, daß dabei die /RD Leitung nicht aktiv wird. Falls ich den Schaltplan der CPS richtig verstanden habe, ist der Datenbus über einen 74LS245 gepuffert. Wenn jetzt aber im Moment der Ausgabe des Vektors auf den Datenbus die /RD Leitung nicht aktiv ist, so treibt der 245 in Richtung Peripherie und nicht in Richtung CPU??? Wie bekommt die CPU den Vektor? Weiter wird der Abschluß der Interruptbehandlungsroutine in der CPU mit dem RETI Befehl signalisiert. Der Peripheriebaustein wartet, bis er auf dem Datenbus einen RETI-Befehl (ED 4D) sieht. Erst dann setzt er den Ausgang IEO wieder auf High und gibt damit die Daisy Chain frei. Aber kann der Peripheriebaustein die beiden Bytes des RETI überhaupt sehen, da ja wieder der 245 dazwischensitzt und vermutlich gerade hochohmig ist, da der RETI Befehl mit /MREQ aus dem Speicher geholt wird. Für etwas Hilfe meinen Knoten zu zerschlagen, wäre ich dankbar.  Viele Grüße netmercer |

||

Beiträge: 52 | Mitglied seit: April 2017 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 30. Oktober 2017 22:14 (#53)

Erstellt am 30. Oktober 2017 22:14 (#53)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo netmercer, (echte Vornamen finde ich besser)

Du hast natürlich vollkommen Recht! Darum gab es den zusätzlichen IC11 (74LS27) in rev.f. Damit wird nun bewerkstelligt (hoffentlich), dass der Datenbustreiber Die Daten immer zur CTC etc. durchgibt und nur in folgenden Fällen Daten auf den BUS sendet: 1. IEI=H, IEO=L, /IORQ=L und /M1=L 2. /ModS=L und /RD (ModS ist /IORQ + richtige Adresse)  Damit müsste "die Kuh vom Eis sein". Das ist bei den Prototypen noch nicht dabei, darum habe ich für den ersten Test den Datenbustreiber gebrückt. Das Problem war also schon erkannt. Trotzdem: Danke für's mitdenken! VG Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 31. Oktober 2017 14:03 (#54)

Erstellt am 31. Oktober 2017 14:03 (#54)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin in die Runde,

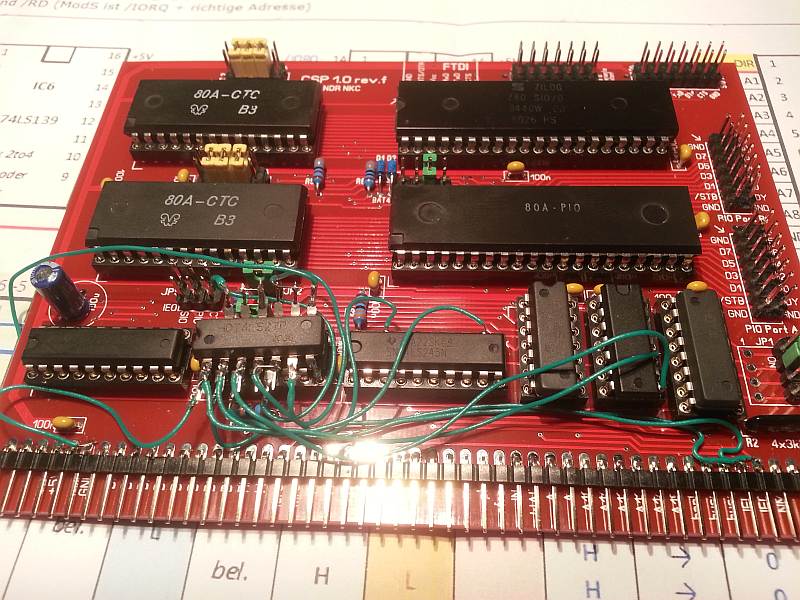

der erste Interrupttest war nach einigen Bauschmerzen auch OK. Mir war völlig entfallen: spätestens vor dem RETI muss erneut ein EI stehen! Sonst bleibt die /INT-Leitung auf Low bis die CPU ein EI liest. Zwei Interrupts in der ersten CTC laufen ohne Probleme gleichzeitig.   Heut Nachmittag werde ich noch die 2. CTC mit einbinden. Wie gesagt: alles noch ohne Datenbustreiber! (der Prototyp Rev.f halt) Wenn die Interrupts 2 CTC's und die PIO laufen, werde ich die Schaltung mit dem Datenbustreiber testen. VG Steffen Nachtrag: CTC2 als 3. Interrupt läuft!  |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

netmercer Kennt sich schon aus   ID # 176 |

Erstellt am 31. Oktober 2017 23:56 (#55)

Erstellt am 31. Oktober 2017 23:56 (#55)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo Steffen,

vielen Dank für die detaillierte Erklärung zur Interruptbehandlung und Kompliment wie Du das umgesetzt hast. Die ersten Tests scheinen ja auch erfolgreich zu laufen.  Ähh, ich hätte da noch eine Frage/Anmerkung zur Baudratengenerierung für die Z80-SIO: Falls ich die gepostete Tabelle richtig deute, so soll die von der CTC Kaskade ausgegebene Taktrate 1:1 als Baudrate für Senden/Empfangen im SIO verwendet werden. Meines Wissens besitzt die SIO aber eigene zuschaltbare Vorteiler (X16, X32, X64), die auch verwendet werden sollten. Dies ist bei asynchroner Übertragung üblich und bei der SIO bauartbedingt erforderlich, da die Z80-SIO ohne internen Vorteiler nicht in der Lage ist, den optimalen Abfragezeitpunkt (sollte ungefähr in der Mitte eines Bits liegen) selbst zu bestimmen. (Bei Synchronbetrieb oder asynchronem Senden kann mit X1 gearbeitet werden) Folglich wäre die Kaskadierung der CTCs nicht erforderlich und 1 CTC pro SIO Kanal würde ausreichen, um alle wichtigen Baudraten aus einer Oszillatorfrequenz von 1,8432 MHz erzeugen zu können. CTC SIO Baudrate 2 .. X16 57600 3 .. X16 38400 4 .. X16 28800 6 .. X16 19200 8 .. X16 14400 12 . X16 9600 16 . X16 7200 24 . X16 4800 32 . X16 3600 48 . X16 2400 64 . X16 1800 96 . X16 1200 192 X16 600 192 X32 300 192 X64 150 Viele Grüße Bernhard (echter Vorname)  |

||

Beiträge: 52 | Mitglied seit: April 2017 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 01. November 2017 08:10 (#56)

Erstellt am 01. November 2017 08:10 (#56)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo Bernhard,

(besser!) (besser!)siehst Du, soweit war ich noch gar nicht. Wenn jeweils ein CTC-Kanal genügt - umso besser! Aber das ist ja gottlob nur ein Softwareproblem und hat keinen Einfluss auf das Layout. Die CTC-SIO-Kopplung mache ich über Jumper, damit ist noch "alles möglich". Ich muss mich sowieso in den nächsten Tagen mit der SIO befassen um diese in der CSP testen zu können. Hab zwar vor 30 Jahren schon eine Datenübertragung syncron, wie auch asyncron mit eigenen Ansätzen in Richtung TCPIP (ohne je etwas von TCTIP gehört zu haben) hinbekommen, aber das ist eben schon lange her.  VG Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 03. November 2017 18:27 (#57)

Erstellt am 03. November 2017 18:27 (#57)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo in die Runde,

die notwendige Änderung, um den Datenbustreiber für die INT-Vektor-Abfrage korrekt zu steuern habe ich eben getestet. (Der 74LS27 huckepack  ) )Der Umbau sieht ziemlich "schmerzhaft" aus....aber es funktioniert, so wie erwartet. Die CTC-Interrupts laufen und senden ihren INT-Vekt. brav an die CPU.   Jo, dann schau ich mal noch ob die Interrupts PIO/SIO laufen. ...und dann kann die CSP 1.0 rev.g (Beitrag #50) in Produktion gehen. VG Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 05. November 2017 13:23 (#58)

Erstellt am 05. November 2017 13:23 (#58)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin in die Runde,

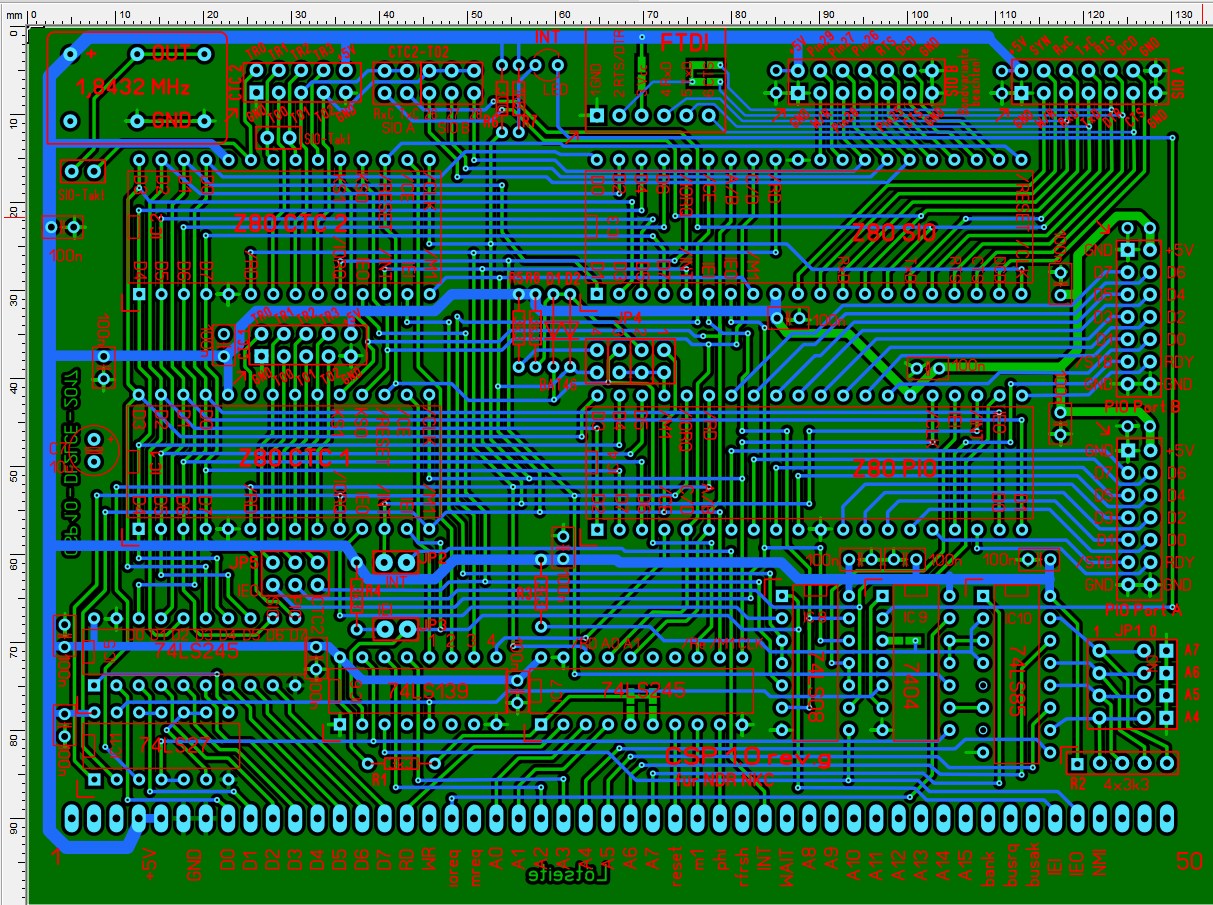

nach den letzten Tests und Erfahrungen habe ich nun den Rev.Stand "h" der CSP fertig gestellt. Da an der oberen Kante durch den Oszillator der Platz sehr eng geworden ist, ich mit der FTDI-Schnittstelle keinerlei Erfahrungen habe und auch keine Rückmeldungen kamen, habe ich diese wieder entfernt. Damit entspannt sich die Platzsituation erheblich. Man kann ja später ggf. mit Aufsatzplatinen für FTDI und oder MAX232 arbeiten. Dann bleibt noch alles offen. Für alle die evtl. Interesse an der Platine haben, hier das letzte Layout. Ich denke in dieser Woche noch den Interruptest PIO und SIO abschließen zu können. Wenn möglich sollte die Platine dann zügig in Produktion gehen. Letzte Wünsche, Korrekturen, Fehlermeldungen etc. sind erwünscht. Wer Platinen davon haben möchte, kann sich hier oder per PN schon mal melden. VG Steffen  |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

Steffen.111 Kennt sich schon aus   ID # 184 |

Erstellt am 07. November 2017 18:14 (#59)

Erstellt am 07. November 2017 18:14 (#59)

Zitat Zitat

PN PN  E-Mail E-Mail

Moin in die Runde,

es ist vollbracht! Ich habe eben die SIO zu einem Rx-INT überreden können. Gesendete Zeichen wurden empfangen und per Interrupt ausgelesen. Dabei lief noch immer der CTC-Interrupt. Jo, es funktioniert! Wenn ich die das neue Platinen-Layout keine neuen Fehler eingebaut habe, dann kann es mit der Produktion los gehen! VG Steffen |

||

Beiträge: 140 | Mitglied seit: August 2017 | IP-Adresse: gespeichert | |||

|

netmercer Kennt sich schon aus   ID # 176 |

Erstellt am 07. November 2017 22:23 (#60)

Erstellt am 07. November 2017 22:23 (#60)

Zitat Zitat

PN PN  E-Mail E-Mail

Hallo Steffen,

Gratulation, schöne Karte entwickelt. Bitte für mich auch eine CSP Platine vormerken. Viele Grüße Bernhard |

||

Beiträge: 52 | Mitglied seit: April 2017 | IP-Adresse: gespeichert |

| https://hschuetz.selfhost.eu | Boardregeln | Datenschutzerklärung

Tritanium Bulletin Board 1.8

© 2010–2021 Tritanium Scripts

Seite in 0,084045 Sekunden erstellt

19 Dateien verarbeitet

gzip Komprimierung eingeschaltet

3489,91 KiB Speichernutzung